- نظرة عامة

- تفاصيل

- موصى به

CY801 مستقبل الترددات اللاسلكية IC مجموعة شرائح الدوائر المتكاملة 300 ميجاهرتز - 450 ميجاهرتز

US$ 0.3

100–999 قِطَع

US$ 0.28

≥1000 قِطَع

مدة التجهيز: 10 – 30 أيام

نوع العمل: مصدر, الشركة المصنعة, بائع على الإنترنت, شركة تجارية

High

معدل الاستجابة

24–48 h

وقت الاستجابة

150 إلى 199

الموظفون

منشور الشركة/المنتج

924.37 KB

سياسة العينات

معلومات المنتج

وصف عام

CY801 عبارة عن شريحة واحدة ASK/OOK (ON-OFF Keyed) جهاز استقبال RF IC. هذا الجهاز هو هوائي حقيقي-في جهاز متجانس خارج البيانات. كل الترددات اللاسلكية وإذا تم ضبط تلقائيا داخل جانبها ، مما يلغي الضبط اليدوي ويقلل من تكلفة الإنتاج. كل ما إذا كان يتم توفير تصفية البيانات وما بعد الكشف (المستخلص) داخل الجانب IC ، لذلك لا توجد فلاتر خارجية ضرورية. واحد من أربعة عروض النطاق الترددي مرشح المستخلص يمكن اختيارها خارجيا من قبل المستخدم. والنتيجة هي حل موثوق للغاية ومنخفض التكلفة. الجهاز مزود بمجموعة من القيم التي يمكن تحديدها بسهولة ، استنادًا إلى معدل البيانات وتنسيق تعديل الكود وتشغيل دورة العمل المطلوبة.

يوفر CY801 وضعين للتشغيل. الوضع الثابت (الإصلاح) ووضع المسح (SWP) ، CY801 يعمل فقط في الوضع الثابت (الإصلاح). في الوضع الثابت ، وظيفتها كمستقبل تقليدي فائق مغاير. في وضع الاجتياح CY801 يكتسح طيف الترددات اللاسلكية أوسع. يوفر الوضع الثابت أداءً أفضل من الانتقائية والحساسية ويتيح وضع المسح استخدام CY801 بتكلفة منخفضة وأجهزة إرسال غير دقيقة.

الميزات

تردد من 300MHz إلى 450 MHz

الجهد. 3.3V-5.5V

حساسية.-حساسية 106dBm ، 1kbps و BER 10-02

معدل بيانات يصل إلى 8 كيلو بايت في الثانية (وضع ثابت)

استهلاك منخفض للطاقة

2.7mA تعمل بكامل طاقتها (315MHz)

3.7mA تعمل بكامل طاقتها (433MHz)

0.9μA في الاغلاق

250μA في عملية استطلاع (دورة عمل 10than1)

إعادة إشعاع الترددات اللاسلكية منخفضة جدًا عند الهوائي

متكاملة للغاية مع عدد جزء خارجي منخفض للغاية

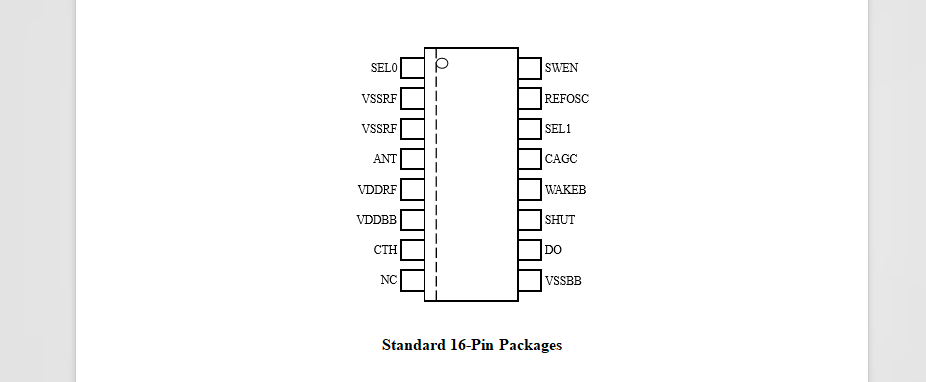

تكوين دبوس

| رقم دبوس 16 دبوس كجم. | اسم دبوس | وظيفة دبوس |

| 1 | SEL0 | Bandwidth selection Bit 0 (Digital Input): Used in conjunction with SEL1 to set the desired demodulator filter bandwidth. See Table 1. Internal pulled-up to VDDRF |

| 2,3 | VSSRF | RF Power Supply: Ground return to the RF section power supply. |

| 4 | ANT | Antenna (Analog Input): For optional performance the ANT pin should be impedance matched to the antenna. See “Applications Information” for information on input impedance and matching techniques. |

| 5 | VDDRF | RF Power Supply: Positive supply input for the RF section of the IC. |

| 6 | VDDBB | Base-band power supply: positive supply input for the baseband section (digital section) of the IC. |

| 7 | CTH | Data slicing threshold capacitor (Analog I/O): capacitor connected to this pin extracts the dc average value from the demodulated waveform which becomes the reference for the internal data slicing comparator. |

| 8 | NC | Not internally connected |

| 9 | VSSBB | Base-Band Power Supply: Ground return to the baseband section power supply. |

| 10 | DO | Data Output ( Digital Output) |

| 11 | SHUT | Shutdown (Digital Input): Shutdown-mode logic-level control input. Pull low to enable the receiver. Internally pulled-up to VDDRF |

| 12 | WAKEB | Wakeup (Digital Output): Active-low output that indicates detection of an incoming RF signal. |

| 13 | CAGC | Automatic Gain Control (Analog I/O): Connect an external capacitor to set the attack/ decay rate of the on-chip automatic gain control. |

| 14 | SEL1 | Bandwidth Section Bit1 (Digital Input): Used in conjunction with SEL0 to set the desired demodulator filter bandwidth. See Table 1. Internally pulled-up to VDDRF. |

| 15 | RFFOSC | Reference Oscillator: Timing reference, sets the RF receive frequency. |

| 16 | SWEN | Sweep-Mode Enable (Digital Input): Sweep or fixed mode operation control input. SWEN high= sweep mode; SWEN low= conventional superheterodyne receiver. Internally pulled-up to VDDRF. |

Technical Specification

749.15kb

معلومات الشحن

- ميناء FOB: شنتشن

- مدة التجهيز: 10–30 أيام

- الوزن لكل وحدة: 0.01 كيلوغرامات

- الابعاد لكل وحدة: 1.0 x 0.5 x 0.1 سنتيمترات

- رمز US HTS: 8517.70.90 00

- وحدات في علبة التصدير: 3000.0

- ابعاد علبة التصدير: 42.0 x 30.5 x 21.0 سنتيمترات

- وزن علبة التصدير: 6.5 كيلوغرامات

أساسيات الأسواق الخارجية

- - آسيا

- - أستراليا

- - وسط/أمريكا الجنوبية

- - أوروبا الشرقية

- - منتصف الشرق/أفريقيا

- - أمريكا الشمالية

- - أوروبا الغربية

المزيد من هذا المورد

-

CYF119B 300M-450MHz ASK جهاز إرسال الترددات اللاسلكية RF مجموعة رقاقات IC للدائرة المتكاملةUS$ 0.18 - 0.191000 قِطَع (أقل كمية للطلب)

CYF119B 300M-450MHz ASK جهاز إرسال الترددات اللاسلكية RF مجموعة رقاقات IC للدائرة المتكاملةUS$ 0.18 - 0.191000 قِطَع (أقل كمية للطلب) -

CY610R 300M-450MHz ASK RF مستقبل دائرة متكاملة IC رقاقةUS$ 0.43 - 0.451000 قِطَع (أقل كمية للطلب)

CY610R 300M-450MHz ASK RF مستقبل دائرة متكاملة IC رقاقةUS$ 0.43 - 0.451000 قِطَع (أقل كمية للطلب) -

CYF4455B 300M-450MHz ASK جهاز إرسال الترددات اللاسلكية RF دائرة متكاملة IC رقاقةUS$ 0.18 - 0.191000 قِطَع (أقل كمية للطلب)

CYF4455B 300M-450MHz ASK جهاز إرسال الترددات اللاسلكية RF دائرة متكاملة IC رقاقةUS$ 0.18 - 0.191000 قِطَع (أقل كمية للطلب) -

CY800 300 ميجاهرتز - 450 ميجاهرتز مستقبل الترددات اللاسلكية IC مجموعة شرائح الدوائر المتكاملةUS$ 0.28 - 0.30100 قِطَع (أقل كمية للطلب)

CY800 300 ميجاهرتز - 450 ميجاهرتز مستقبل الترددات اللاسلكية IC مجموعة شرائح الدوائر المتكاملةUS$ 0.28 - 0.30100 قِطَع (أقل كمية للطلب) -

CY600R 300M-450MHz ASK مستقبل RF دائرة متكاملة IC رقاقةUS$ 0.43 - 0.451000 قِطَع (أقل كمية للطلب)

CY600R 300M-450MHz ASK مستقبل RF دائرة متكاملة IC رقاقةUS$ 0.43 - 0.451000 قِطَع (أقل كمية للطلب) -

CY318 300M-450MHz ASK مستقبل RF رقاقة IC للدائرة المتكاملةUS$ 0.18 - 0.191000 قِطَع (أقل كمية للطلب)

CY318 300M-450MHz ASK مستقبل RF رقاقة IC للدائرة المتكاملةUS$ 0.18 - 0.191000 قِطَع (أقل كمية للطلب) -

CY590 300M-450MHz ASK RF مستقبل دارة متكاملة IC Chipset - مكون إلكتروني للتحكم عن بعد لاسلكيUS$ 0.18 - 0.201000 قِطَع (أقل كمية للطلب)

CY590 300M-450MHz ASK RF مستقبل دارة متكاملة IC Chipset - مكون إلكتروني للتحكم عن بعد لاسلكيUS$ 0.18 - 0.201000 قِطَع (أقل كمية للطلب)

منتجات ذات صلة من موردين آخرين

-

خط الطاقة هو خط البيانات الخاص بك. وحدة الاتصالات عبر خطوط الطاقة (PLC) المدمجة JMN-L80A تلغي الحاجة إلى أسلاك مخصصة.US$ 9.70 - 10.002 قِطَع (أقل كمية للطلب)

خط الطاقة هو خط البيانات الخاص بك. وحدة الاتصالات عبر خطوط الطاقة (PLC) المدمجة JMN-L80A تلغي الحاجة إلى أسلاك مخصصة.US$ 9.70 - 10.002 قِطَع (أقل كمية للطلب) -

قطع إلكترونية جديدة وأصلية | موزع مكونات إلكترونيةUS$ 0.1010 قِطَع (أقل كمية للطلب)

قطع إلكترونية جديدة وأصلية | موزع مكونات إلكترونيةUS$ 0.1010 قِطَع (أقل كمية للطلب) -

حار بيع الأصلي الالكترونيات PEF2256HV2.1 الاتصالات المتكاملة Framer ، وحدة واجهة الخط (LIU) P-MQFP-80-1US$ 1.00 - 2.001 قِطَع (أقل كمية للطلب)

حار بيع الأصلي الالكترونيات PEF2256HV2.1 الاتصالات المتكاملة Framer ، وحدة واجهة الخط (LIU) P-MQFP-80-1US$ 1.00 - 2.001 قِطَع (أقل كمية للطلب) -

INA139NA/3K Merrillchip جديد أصلي في المخزن مكونات إلكترونية دارة متكاملةUS$ 0.65 - 1.3510 قِطَع (أقل كمية للطلب)

INA139NA/3K Merrillchip جديد أصلي في المخزن مكونات إلكترونية دارة متكاملةUS$ 0.65 - 1.3510 قِطَع (أقل كمية للطلب) -

لوحة دارات مطبوعة لقارئ RFID لتصميم المنتجات الإلكترونية الذكية، تصميم الأجهزة والبرامج، تطوير برامج MCU بتردد 13.56 ميجاهرتزUS$ 1.10 - 2.001 الوحدات (أقل كمية للطلب)

لوحة دارات مطبوعة لقارئ RFID لتصميم المنتجات الإلكترونية الذكية، تصميم الأجهزة والبرامج، تطوير برامج MCU بتردد 13.56 ميجاهرتزUS$ 1.10 - 2.001 الوحدات (أقل كمية للطلب) -

لوحة دوائر مطبوعة مخصصة للاتصالات عبر الأقمار الصناعية: خدمات OEM لتجميع الدوائر المتكاملة للميكروويف عالية الموثوقيةUS$ 5.00 - 500.001 كرتون (أقل كمية للطلب)

لوحة دوائر مطبوعة مخصصة للاتصالات عبر الأقمار الصناعية: خدمات OEM لتجميع الدوائر المتكاملة للميكروويف عالية الموثوقيةUS$ 5.00 - 500.001 كرتون (أقل كمية للطلب) -

مكونات إلكترونية أصلية لشبكة الاتصالات رقائق IC رقم الجزء LM5122ZPWPRUS$ 0.105 قِطَع (أقل كمية للطلب)

مكونات إلكترونية أصلية لشبكة الاتصالات رقائق IC رقم الجزء LM5122ZPWPRUS$ 0.105 قِطَع (أقل كمية للطلب)